Jhonny Novillo Vicuña, Dixys Hernández Rojas

Universidad Técnica de Machala

# Fundamentos de los Sistemas Microprocesados II

# Ing. César Quezada Abad, MBA **RECTOR**

Ing. Amarilis Borja Herrera, Mg. Sc. **Vicerrectora Académica**

Soc. Ramiro Ordóñez Morejón, Mg. Sc. **VICERRECTOR ADMINISTRATIVO**

COORDINACIÓN EDITORIAL VICERRECTORADO ACADÉMICO

Tomás Fontaines-Ruiz, PhD.

Investigador Becario Prometeo-Utmach

Asesor Del Programa De Reingeniería

Ing. Karina Lozano Zambrano

COORDINADORA EDITORIAL

Ing. Jorge Maza Córdova, Ms. Ing. Cyndi Aguilar **EQUIPO DE PUBLICACIONES**

# Fundamentos de los Sistemas Microprocesados II

Johnny Novillo Vicuña Dixys Hernández Rojas

## Dedicatoria

A nuestras familias, quienes son nuestra inspiración y fortaleza de todos los días, y a nuestros queridos estudiantes, compañeros permanentes en nuestro aprendizaje.

Los autores

## Agradecimiento

A Karina y sus compañeros del Octavo Semestre, Paralelo A, de la Carrera de Ingeniería de Sistemas de la Universidad Técnica de Machala, por su valioso aporte para el desarrollo del presente libro. Los autores

Primera edición 2015

ISBN Obra completa: 978-9978-316-99-3

ISBN: 978-9942-24-006-4

D.R. © 2015, UNIVERSIDAD TÉCNICA DE MACHALA Ediciones UTMACH Km. 5 1/2 Vía Machala Pasaje www.utmachala.edu.ec

ESTE TEXTO HA SIDO SOMETIDO A UN PROCESO DE EVALUACIÓN POR PARES EXTERNOS CON BASE EN LA NORMATIVA EDITORIAL DE LA UTMACH.

Portada:

Concepto editorial

Samanta Cabezas (EST. COMUNICACIÓN SOCIAL) Fotografía: Dir. de Comunicación UTMACH

Diseño, montaje y producción editorial: UTMACH

Impreso y hecho en Ecuador Printed and made in Ecuador

Advertencia: "Se prohíbe la reproducción, el registro o la transmisión parcial o total de esta obra por cualquier sistema de recuperación de información, sea mecánico, fotoquímico, electrónico, magnético, electroóptico, por fotocopia o cualquier otro, existente o por existir, sin el permiso previo por escrito del titular de los derechos correspondientes".

# Índice

| Introducción                                               | 15 |

|------------------------------------------------------------|----|

| Conexión de memorias al microprocesador                    | 17 |

| Criterios para selección de memorias                       | 18 |

|                                                            | 21 |

| Conexión de la memoria de datos                            | 25 |

| Conexión completa de memorias en un sistema microprocesado |    |

|                                                            | 29 |

| El microprocesador 8085                                    | 35 |

| Caracterización interna del microprocesador 8085           | 36 |

| Arquitectura                                               | 36 |

| Registros                                                  | 38 |

| Unidad Aritmética Lógica                                   | 39 |

| Unidad de control de Señales                               | 41 |

| Control de Interrupciones                                  | 42 |

| Control de Entrada/salida serie                            | 43 |

| Descripción de pines                                       | 44 |

| Introducción a la programación del microprocesador 8085    | 46 |

| Ciclos de máquina                                          | 48 |

| Operación búsqueda de código de operación (opcode fetch)   | 48 |

| Operación de ciclo lectura de memoria                      | 49 |

| Operación de ciclo escritura de memoria                    | 50 |

| Modos de direccionamientoa                                 | 51 |

| Direccionamiento implicado                           | 51 |

|------------------------------------------------------|----|

| Direccionamiento de registro                         | 51 |

| Direccionamiento inmediato                           | 52 |

| Direccionamiento directo                             | 52 |

| Direccionamiento indirecto de registro               | 53 |

| Repertorio de instrucciones del microprocesador 8085 | 53 |

| MOV r1, r2 (Transfiere registro)                     | 59 |

| MOV r, M (Transfiere de memoria)                     | 60 |

| MOV M, r (Transfiere a memoria)                      | 60 |

| MVI r, dato (Transferencia inmediata)                | 61 |

| MVI M, dato (Transfiere a memoria inmediata)         | 61 |

| LXI rp, dato 16 (Carga registro par inmediato)       | 61 |

| LDA addr (Carga acumulador directo)                  | 62 |

| STA addr (Almacena acumulador directo)               | 62 |

| LHLD addr (Carga H y L directo)                      | 63 |

| SHLD addr (Almacena H y L directo)                   | 63 |

| LDAX rp (Carga indirecto el acumulador               | 64 |

| STAX rp (Almacena indirecto el acumulador)           | 64 |

| XCHG (Intercambia H y L con D y E)                   | 65 |

| Grupo aritmético                                     | 65 |

| ADD r, (Suma Registros)                              | 70 |

| ADD m, (Suma Memoria)                                | 70 |

| ADI dato, (Suma Inmediata)                           | 70 |

| ADC r, (Suma Registro con arrastre)                  | 71 |

| ADC m, (Suma memoria con arrastre)                   | 71 |

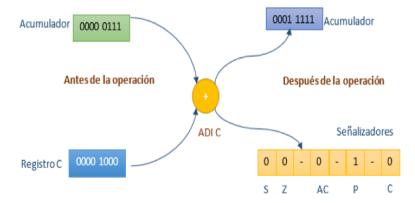

| ACI dato, (Suma inmediata con arrastre)              | 72 |

| SUB r, (Resta Registros))                            | 72 |

| SUB m, (Resta Memoria)                               | 72 |

| SUI dato, (Resta Inmediata)                          | 73 |

| SBB r, (Registro con préstamo)                       | 73 |

| SBB m, (Resta memoria con préstamo)                  | 74 |

| INR r, (Incrementa Registro)                         | 74 |

| INR M, (Incrementa Memoria)                          | 75 |

| DCR r, (Decrementar Registro)                        | 75 |

| DCR m, (Decrementa memoria)                          | 75 |

| INX rp, (Incrementa registro par))                   | 76 |

|                                                      |    |

| DCX rp, (Decrementa registro par)                              | 76    |

|----------------------------------------------------------------|-------|

| DAD rp, (Suma registro par a H y L)                            | 77    |

| DAA (Ajuste decimal acumulador)                                | 77    |

| Grupo lógico                                                   | 78    |

| ANA r (AND registro)                                           | 81    |

| ANA M (AND Memoria)                                            | 82    |

| ANI dato (AND Inmediato)                                       | 82    |

| ORA r (OR registro)                                            | 83    |

| ORA M (OR Memoria)                                             | 83    |

| ORI dato (OR Inmediato)                                        | 84    |

| XRA r (OR Exclusiva registro)                                  | 84    |

| XRA M (OR Exclusiva memoria)                                   | 85    |

| XRI Dato (OR Exclusiva inmediata)                              | 85    |

| CMP r (Compara registro)                                       | 86    |

| CPI Dato (Comparación inmediata)                               | 86    |

| CMP M (Compara memoria)                                        | 87    |

| RLC (Desplazamiento circular a la izquierda)                   | 87    |

| RRC (Desplazamiento circular a la derecha)                     | 88    |

| RAL (Desplazamiento circular a la izquierda a través de la     |       |

| arrastre)                                                      | 88    |

| RAR (Desplazamiento circular a la derecha a través de la arras | stre) |

|                                                                | 89    |

| CMA (Complementa el Acumulador)                                | 89    |

| STC (Pone a 1 el arrastre)                                     | 89    |

| CMC (Complementa arrastre)                                     | 90    |

| Grupo de bifurcación                                           | 90    |

| JMP addr (Salto)                                               | 93    |

| JCondition addr (Salto condicional))                           | 93    |

| CALL addr (Llamada)                                            | 94    |

| Ccondition addr (Llamada condicional)                          | 95    |

| RET (Vuelta)                                                   | 96    |

| RCondition (Vuelta condicional)                                | 96    |

| RST n (Rearrancar)                                             | 97    |

| PCHL n (Salta indirecto H y L – transfiere H y L a PC)         | 97    |

| Grupo de pila, E/S y control máquina                           | 106   |

| PUSH rp, dato (Introducir)                                     | 108   |

|                                                                |       |

| PUSH PSW                                             | 109 |

|------------------------------------------------------|-----|

| POP rp, dato (Sacar)                                 | 109 |

| POP PSW                                              | 110 |

| XTHL (Intercambiar tope de la pila con H y L)        | 111 |

| SPHL (Transferir HL a SP)                            | 111 |

| IN puerto (Entrar)                                   | 112 |

| OUT puerto (Salir)                                   | 112 |

| EI (Habilita interrupciones)                         | 113 |

| DI (Inhabilita interrupciones)                       | 113 |

| HLT (Alto)                                           | 114 |

| NOP (No operación)                                   | 114 |

| RIM                                                  | 115 |

| SIM                                                  | 115 |

|                                                      |     |

| Glosario                                             | 119 |

|                                                      |     |

| Anexos                                               | 123 |

|                                                      |     |

| A - 2 - 12                                           | 405 |

| Apéndices                                            | 127 |

|                                                      |     |

| Bibliografia                                         | 133 |

|                                                      |     |

| Índices de cuadros, gráficas, imágenes y fotografías | 135 |

| Índice de cuadros                                    | 135 |

| Índice de gráficas                                   |     |

| 3                                                    |     |

| Biografia                                            | 137 |

| $\epsilon$                                           |     |

### Introducción

Éste segundo Tomo, de la colección Fundamentos de los Sistemas Microprocesados, constituye una fuente de información importante para quienes desean aprender cómo conexionar memorias a un microprocesador, así como también, cómo desarrollar un programa en lenguaje ensamblador, para que un microprocesador ejecute las instrucciones necesarias para implementar un sistema microprocesado específico.

A continuación se detalla el contenido del presente Tomo:

- Capítulo I Conexión de memorias al microprocesador: Comprende 4 temáticas: criterios de selección de memorias, conexión de la memoria de programa y de datos, finalizando con la presentación de las mismas, en una conexión completa en un sistema microprocesado.

- CAPÍTULO II El microprocesador 8085: Estructurado en 4 temáticas enfocadas al estudio del microprocesador 8085; abarcando su caracterización interna, introducción a la programación, repertorio de instrucciones y aplicaciones de programación. Si bien es cierto que el contenido de éste capítulo está enfocado al estudio respecto al hardware y software del microprocesador 8085, esto no le resta actualidad al libro, ya que para incursionar en el estudio de un microprocesador de última tecnología, se requiere conocer los fundamentos de operación que tuvieron los microprocesadores iniciales.

Conforme realice la lectura se encontrará con símbolos que le ayudarán a entender mejor el tema, evaluar sus conocimientos y reforzar lo aprendido mediante fuentes alternas para complementar ciertos temas. Entre los símbolos establecidos se encuentran:

#### Sabías que...

Presenta un enfoque que los autores realizan sobre una temática relacionada al tema central o sobre algún dato curioso propicio en el contenido.

#### Resuelve

Preguntas de reflexión que le ayudarán a reforzar su conocimiento del tema.

#### Bibliografía y Fuentes Electrónicas

Bibliografía y fuentes electrónicas que le ayudarán a complementar el tema tratado.

Ejemplo

Enunciado de ejemplo práctico sobre la temática correspondiente.

Solución

La solución del ejercicio que se ha enunciado en Ejemplo.

Ejercicios Propuestos

Problemas planteados con la finalidad de desarrollar la independencia cognoscitiva del lector, respecto del tema tratado.

## Conexión de memorias al microprocesador

### Objetivos

- Determinar los criterios más relevantes para la selección de memorias a utilizarse en un sistema microprocesado específico.

- Analizar las principales características de la EPROM 27256, a través del estudio de las señales que la componen, para realizar la conexión de ésta memoria de programa con el microprocesador.

- Analizar las principales características de la SRAM 6116, a través del estudio de las señales que la componen, para realizar la conexión de ésta memoria de datos con el microprocesador.

- Realizar la conexión completa de la memoria de programa y de datos con un microprocesador analizando adecuadamente sus señales.

#### Introducción

El presente Capítulo se enfoca en la enseñanza del proceso de identificación de las memorias que son compatibles con un microprocesador, de acuerdo a su capacidad de memoria direccionable, el voltaje de alimentación que necesita para funcionar y el número de bits de datos y de direcciones que poseen.

El microprocesador deberá tener una conexión con dos tipos de memoria, la memoria de datos y la memoria de programa. Cabe advertir que además se suelen requerir otros chips, ya sea para decodificar señales, o en el caso de que el microprocesador que se esté usando tenga un bus de datos multiplexado, se demandará de un cerrojo, que permita identificar cuáles bits del microprocesador son de datos y cuáles de direcciones.

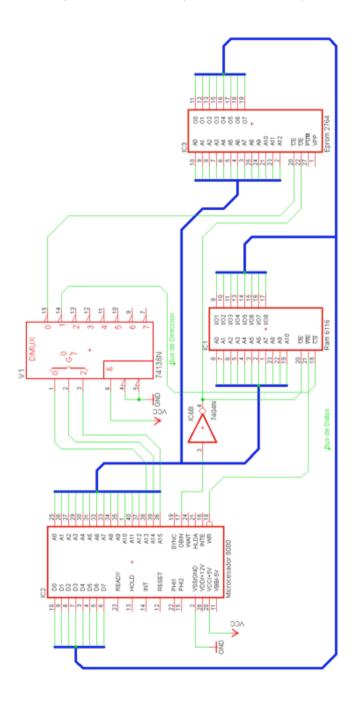

Se tomarán como referencia para la interconexión completa de un sistema microprocesado, los chips de memoria SRAM 6116, EPROM 27256 y el microprocesador de Intel 8085; además de los chips 74374 (LATCH) y 74138 (decodificador).

Los diagramas y esquemas que se presentan, fueron elaborados en un programa de versión gratuita, el Light Edition EAGLE versión 7.5.0

## Criterios para selección de memorias

El microprocesador y los chips de memoria son elementos primordiales en la construcción de sistemas microprocesados, razón por la cual, es importante definir criterios de selección que garanticen la compatibilidad de los mismos con el microprocesador que se vaya a utilizar. A continuación se establecen algunos de los criterios más importantes:

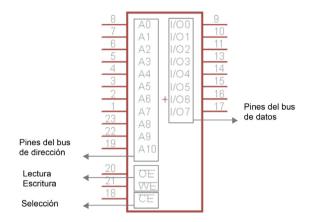

• Pines del bus de direcciones: Son aquellos que sirven para conocer la posición de un dato. Son unidireccionales y permiten acceder al bus de direcciones para leer alguna ruta específica.

El tipo de señales que se transmite por estos pines, suele ser solo direcciones, pero en algunos microprocesadores están multiplexadas, es decir, que las señales podrán ser tanto de direcciones como de datos y en esos casos tocará utilizar un chip especial conocido como "cerrojo o LATCH" para que identifique durante la comunicación con otros chips si se trata de un dato o de una dirección.

- Pines del bus de datos: Son aquellos que se utilizan para la entrada o salida de datos en las memorias, por ende son bidireccionables. Estos además se usan para saber el ancho de palabra que soporta un chip.

- Voltaje de alimentación: En un sistema microprocesado se utiliza normalmente, el mismo voltaje para alimentar a toda la placa de circuitos integrados; por eso es recomendable utilizar memorias que se alimenten con igual voltaje que el microprocesador.

• Mapa de memoria: Indica cómo van a estar ubicadas cada una de las memorias (RAM O ROM) y zonas libres dentro del espacio de direcciones del sistema microprocesado. Este espacio no es otra cosa que la capacidad de memoria direccionable

```

CMD= 2<sup>m</sup> x n

Donde,

m = número de bits de direcciones

n = número de bits de datos

```

Existen otros criterios menos importantes, que se recomiendan tener presentes, ya que podrían influir en el diseño y construcción de un sistema microprocesado. Entre ellos están:

- Señales de selección: Toda memoria tiene una entrada de selección para ser habilitada, que suele ser identificada con las siguientes denominaciones para la RAM: **CS** (chip select), **S** (select), y **CE** (chip enable), y para la ROM se suele encontrar con esta misma nomenclatura o con la letra **E**. Estas entradas se activan por lo general cuando se les envía un cero lógico para las tareas de lectura o escritura de datos.

- Señales de Control: En la RAM las señales de control se las puede encontrar con las siguientes denominaciones: **OE** (output enable) o **G**, y su tarea es transmitir los datos desde las terminales de salida siempre y cuando estén activas. En cambio, la señal que se utiliza para la escritura de datos se representa con las siglas **WE** (writer enable).

En la ROM solo se suele encontrar la señal  $\mathbf{OE}$  debido a que la señal para escritura se encuentra representada por las siglas  $\mathbf{P}$  (program) y  $\mathbf{Vpp}$ , que actúan en conjunto para grabar un dato de manera permanente en la memoria.

En la Figura 1, se presenta un esquema general de un chip de memoria RAM, indicando los pines del bus de direcciones, pines del bus de datos, señales de selección, y señales de control de escritura y lectura.

Figura 1. Terminales de un chip de memoria RAM

Las memorias que se conectan con el microprocesador para la implementación de un sistema microprocesado, pueden ser:

- 1) Memoria de programa: guarda de manera permanente la información. Por ejemplo, la memoria PROM, EPROM, EEPROM. Este tipo de chips se fabrican con capacidades de orden de Kilobytes o Megabytes en múltiplos de 8. Por ejemplo: 2kx8, 8kx8, 16kx8, 32kx8, etc.

- 2) Memoria de datos: almacena la información de manera temporal. Ejemplo, la memoria SRAM, DRAM.

Sabías que...

Los pines de dirección (A0, A1, A2,....An) son importantes en un microprocesador o memoria, pues de acuerdo a la cantidad que exista de ellos, se puede determinar la capacidad de memoria direccionable en KB. Ver Tabla 1.

| Cantidad de pines de dirección | Capacidad de localidades |

|--------------------------------|--------------------------|

| 10 pines (A0 - A9)             | 1 K                      |

| 11 pines (A0 - A10)            | 2 K                      |

| 12 pines (A0 - A11)            | 4K                       |

| 13 pines (A0 - A12)            | 8K                       |

| 14 pines (A0 - A12)            | 16K                      |

| 15 pines (A0 - A12)            | 32K                      |

| 16 pines (A0 - A12)            | 64K                      |

- 1. ¿Pueden separarse los criterios de selección de memoria de acuerdo al tipo (RAM o ROM)?

- 2. ¿Existe otra manera de indicar que las señales de memoria (E, P, OE, etc.) se activan con un cero lógico aparte de resaltarlas en negrita? ;Cuáles?

- 3. ¿Por qué la ROM no cuenta con la señal WR?

- 4. ¿Qué función cumple un LATCH dentro de un sistema microprocesado?

- 5. ¿Cuál sería la capacidad en KB, de una memoria de 18 pines de dirección?

#### Bibliografía y Fuentes Electrónicas

- Benítez, C. (Febrero de 2010). El microprocesador 8085. Microprocesadores, 17. Obtenido de http://issuu.com/microprocesadores/docs/8085\_\_\_1\_

- Electronic Components Datasheet Search. (2015). ALLDATASHEET. COM. Obtenido de http://www.alldatasheet.com/

- Massachusetts Institute of Technology. (2015). mit.com. Obtenido de web.mit.edu/6.115/www/document/6116.pdf

## Conexión de la memoria de programa

La memoria de programa se utiliza para almacenar las instrucciones y datos de manera permanente en un sistema microprocesado. A continuación se detallará cómo conexionar la EPROM 27256 con capacidad de 64Kb (8k x 8), con un microprocesador Intel 8085.

Memoria EPROM 27256

El circuito integrado 27256 es un tipo de memoria eléctricamente programable de solo lectura, que dispone de un bus de datos o ancho de palabra de 8 bits. Se considera una memoria de alta velocidad con tiempos de acceso de 90ns, diseñada con la tecnología CMOS. Trabaja con una fuente de +5.0 Voltios y está comprimida en una pastilla de 28 pines.

Por lo expuesto, se considera a la memoria 27256 compatible para la conexión con el microprocesador 8085. A continuación se detalla la información necesaria para conocer cómo están distribuidas las señales de datos, dirección, selección y control entre los pines del dispositivo.

Memoria EPROM 27256 00 01 02 03 04 A2 A12 A13 Œ Œ EPROM 27256 Pines Descripción De A0 hasta A14 Bus de direcciones De D0 0 hasta D7 Bus de datos GND Terminal de masa o tierra Vcc Terminal de alimentación (+5V) aaV Entrada de programación CE Chip de selección del componente OF Entrada de lectura

Tabla 2. Diagrama de pines de la memoria EPROM 27256

Una vez conocida la distribución de las señales de control y selección, dentro de la memoria 27256, se deben conocer los chips adicionales que se necesitarán para poder comunicarla con el microprocesador 8085. Estos chips son:

74374, conocido también como LATCH o cerrojo, actúa como un traductor de señales que indica a la memoria RAM o ROM si se trata de un dato o de una dirección.

Este chip es necesario cuando se utiliza un microprocesador con el bus de datos/dirección multiplexado. Ver Apéndice A.

74138, actúa como decodificador de señales del microprocesador. La función que cumple es seleccionar, mediante sus salidas, cualquier componente que el microprocesador requiera. Ver Apéndice B.

Cabe recalcar que la información sobre el diseño de un decodificador de direcciones, para un determinado sistema microprocesado, se puede encontrar en el Capítulo 2 del Tomo I, de la presente colección "Fundamentos de los Sistemas Microprocesados".

#### Ejemplo 1-1

Realizar un diagrama de conexión de la memoria de programa EPROM 27256 con el microprocesador 8085.

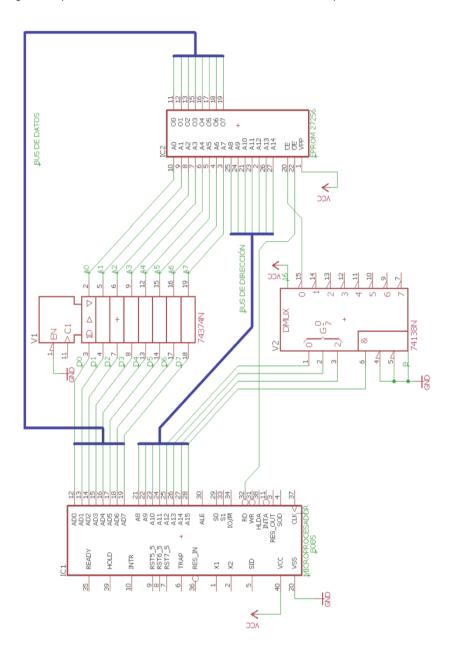

La conexión de la memoria de programa EPROM 27256 con el microprocesador 8085, requerirá adicionalmente de los circuitos integrados 74374 y 74138.

#### Soloución

A continuación se describen las conexiones de los diferentes pines de la memoria EPROM 27256, con cada uno de los dispositivos necesarios para el desarrollo de la interface.

- Conectar las líneas de dirección de A0 hasta A7, con las salidas correspondientes de A0 hasta A7 del 74374.

- Conectar las líneas de dirección de A8 hasta A14, con las líneas correspondientes de A8 hasta A14 del microprocesador.

- Conectar las líneas de datos de O0 hasta O7, con las líneas correspondientes de AD0 hasta AD7 del microprocesador.

- Conectar el pin Vcc a una fuente de alimentación de +5V y el pin de GND a tierra.

- Conectar el pin Vpp a una fuente de alimentación de +5V o puentearlo con la señal Vcc que se alimenta del mismo voltaje.

- Conectar **CE** con la salida correspondiente del decodificador 74138.

- Conectar **OE** con la salida **RD** del microprocesador.

Al realizar el proceso de conexión se debe tener la precaución de conectar de forma adecuada los buses de dirección y de datos de la EPROM, con los correspondientes de los dispositivos complementarios, pues de no ser así, se podrían obtener resultados no esperados.

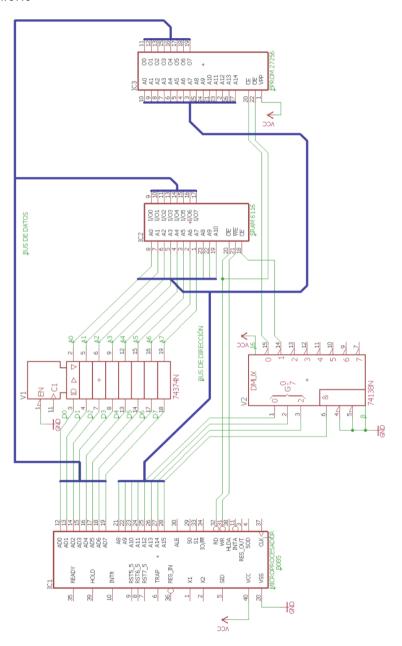

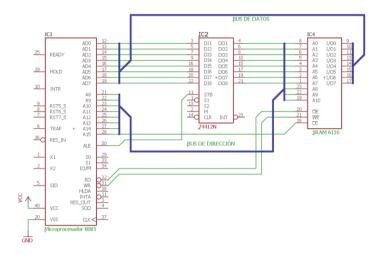

En la Figura 2., se presenta el correspondiente diagrama de conexión: las líneas verdes representan los hilos de conexión y las líneas azules, los buses de datos y direcciones.

Como se puede apreciar, los buses pueden abarcar varios hilos de conexión comunicando varios dispositivos al mismo tiempo.

Figura 2. Esquema de conexión de la memoria EPROM 27256 con el microprocesador 8085

#### Sabías que...

Los modos de programar una memoria ROM varían de acuerdo al tipo de integrado que se esté escogiendo. En muchos casos este ocupa dos entradas de diferente nominación de voltaje, una para que en él, pueda programarse determinado conjunto de datos, y otra para alimentar las demás señales. Por ello es preciso que se consulte la hoja de especificaciones o datasheet del integrado que se usará.

Las variantes se encuentran básicamente en el estado alto (recibe 1 lógico) o bajo (recibe 0 lógico) que deben mantener las señales de control y selección durante el proceso de programación de la ROM, pues se puede presentar el caso de que mientras la señal Vcc reciba +5 V, la Vpp reciba +12 V, y al mismo tiempo se requiera que la señal CE necesite estar en bajo y la OE en alto.

#### Preguntas de reflexión

- 1. ¿Qué señal de la memoria de programa debe ir conectada al decodificador de direcciones?

- 2. ¿Con qué señal del microprocesador debe ir conectada la señal OE de la memoria de programa?

- 3. ¿Por qué razón se utiliza un cerrojo o Latch para un bus multiplexado?

- 4. ¿Qué funciones cumple la señal Vpp?

#### Bibliografía y Fuentes Electrónicas

- Mandado, Enrique y Mandado, Yago (2008). Sistemas Electrónicos Digitales (9 ed.). México: Técnicas – Alfaomega Grupo Editor, S.A.,

- Electronic Components Datasheet Search. (2015). ALLDATASHEET. COM. Obtenido de

http://www.alldatasheet.com/view.jsp?Searchword=M27256

• Benítez, C. (2010). issuu. Obtenido de

http://issuu.com/microprocesadores/docs/8085\_2

#### Conexión de la memoria de datos

Un sistema microprocesado necesita de una memoria temporal en la que se pueda leer y escribir datos cada vez que se ejecute la instrucción correspondiente. A continuación se detallará cómo conexionar la SRAM 6116, con capacidad de 2Kb, con un microprocesador Intel 8085.

Memoria SRAM 6116

El circuito integrado 6116 es un tipo de memoria de acceso aleatorio (RAM), que dispone de una capacidad de 2048 palabras de 8 bits. Se considera una memoria estática de alta velocidad, diseñada

con la tecnología CMOS. Trabaja con una fuente de +5.0 Voltios y está comprimida en una pastilla de 24 terminales o pines.

Esta memoria fue seleccionada por ser compatible con el microprocesador 8085, dado que posee un bus de datos de 8 bits. A continuación, se describe como están distribuidas las señales de control y selección entre los pines.

Tabla 3. Diagrama de pines de la memoria SRAM 6116

| Memoria SRAM 6116          |                       |                                                      |                            |  |  |

|----------------------------|-----------------------|------------------------------------------------------|----------------------------|--|--|

| 8<br>7<br>6                | 40<br>41              | I/00<br>I/01                                         | 9<br>10<br>11              |  |  |

| 22<br>19<br>20<br>21<br>18 | A9<br>A10<br>DE<br>WE | I/O1<br>I/O2<br>I/O3<br>I/O4<br>I/O5<br>I/O6<br>I/O7 | 13<br>14<br>15<br>16<br>17 |  |  |

| Pines                      |                       |                                                      | Descripción                |  |  |

| De A0 hasta A10            |                       | Bus de direcci                                       | ones                       |  |  |

| De I/O 0 hasta I/O7        |                       | Bus de datos                                         |                            |  |  |

| GND                        |                       | Terminal de m                                        | nasa o tierra              |  |  |

| Vcc                        |                       | Terminal de al                                       | limentación (+5V)          |  |  |

| CĒ                         |                       | Chip de selección del componente                     |                            |  |  |

| OĒ                         |                       | Entrada de lec                                       |                            |  |  |

| WE                         |                       | Entrada de esc                                       | critura                    |  |  |

#### Ejemplo 1-2

Realizar un diagrama de conexión de la memoria de datos SRAM 6116 con el microprocesador 8085.

Cabe recalcar que la memoria de datos, también necesita de un LATCH y de un decodificador, para poder interactuar con el microprocesador 8085.

#### Soloución

A continuación se describen las conexiones de los diferentes pines de la memoria RAM 6116, con cada uno de los dispositivos necesarios para el desarrollo de la interface.

- Conectar las líneas de dirección de A0 hasta A7 con las salidas correspondientes de A0 hasta A7 del 74374.

- Conectar las líneas de dirección de A8 hasta A10 con las líneas correspondientes de A8 hasta A10 del microprocesador 8085.

- Conectar las líneas de datos de D0 hasta D7 con las líneas correspondientes de AD0 hasta AD7 del microprocesador 8085.

- Conectar **CE** con la salida correspondiente del decodificador 74138.

- Conectar **WE** con la señal **WR** del microprocesador 8085.

- Conectar **OE** con la salida **RD** del microprocesador 8085.

Cuando han sido conectadas las señales de la memoria de datos, como se indicó anteriormente, el diagrama de conexiones quedaría de la siguiente manera:

Figura 3. Esquema de conexión de la memoria SRAM 6116 con el microprocesador 8085

#### Sabías que...

Las señales de control y selección como WE, OE y CE generalmente se activan en BAJO (0 lógico) cuando suelen estar marcadas en negrita (**WE, OE y CE**), con una línea en la parte superior (**WE, OE y CE**,) o con un apostrofe al final (WE', OE' y CE'). En cambio cuando no están enmarcada de ninguna forma indica que las señales se activan en ALTO (1 lógico).

#### Preguntas de reflexión

- 1. ¿A qué señal del microprocesador debe ir conectada la señal WE de la SRAM 6116?

- 2. ¿Cómo se podría conectar la memoria de datos con el microprocesador 8085 utilizando el circuito integrado 8212?

- 3. ¿Cómo quedaría el diagrama de conexión si se utilizaran memorias de datos con un ancho de palabra de 4 bits?

#### Bibliografía y Fuentes Electrónicas

- Benítez, C. (2010). issuu. Obtenido de http://issuu.com/microprocesadores/docs/8085 2

- Massachusetts Institute of Technology. (2015). mit.com. Obtenido de web.mit.edu/6.115/www/document/6116.pdf

# Conexión completa de memorias en un sistema microprocesado

Existen señales comunes entre los circuitos integrados, tales como: CE y OE. Ahora la pregunta es ¿Qué se debe hacer con las señales que se repiten en los diferentes circuitos integrados, si el microprocesador solo tiene un pin para conectar cada señal en su respectivo lugar?. La respuesta es sencilla, se deben puentear las señales tal como se haría para tomar voltaje de algun hilo que ya se conectó a la fuente. Es decir, una vez que se conecta totalmente un dispositivo, los demás integrados que requieren de la misma señal, lo que hacen es anclarse a la linea que tenga la señal que necesitan.

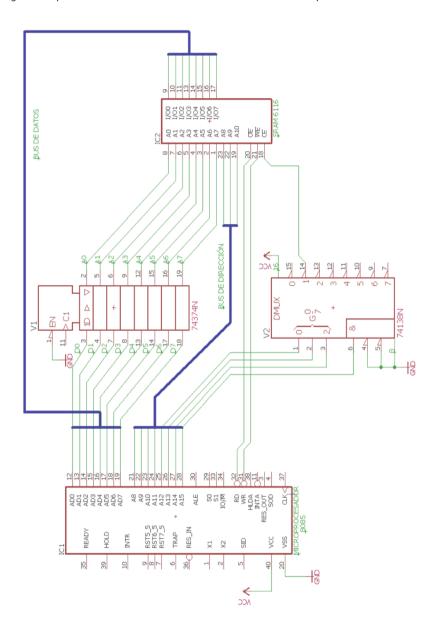

Una vez comprendido como deben ser las conexiones entre las memorias de datos y de programa con el microprocesador, lo único que faltaría es realizar la conexión completa de un sistema microprocesado.

Ejemplo 1-3

Realizar un diagrama de conexión completo de un sistema microprocesado, que tiene como base el microprocesador 8085, además de una memoria de datos 6116, memoria de programa 27256, un LATCH 74374 y un decodificador 74138.

Soloución

A continuación se describe las conexiones de los diferentes pines de los dispositivos anteriormente indicados, con la finalidad de implementar el sistema microprocesado requerido.

Conectar las líneas de dirección de A0 hasta A7 de la SRAM 6116 con las salidas correspondientes de A0 hasta A7 del 74374. Además se deberá conectar desde A8 hasta A10, con los pines de dirección de A8 hasta A10 del microprocesador.

Conectar el bus de direcciones desde A0 hasta A10 de la EPROM 27256 con la línea del bus de direcciones que ya existe.

Conectar mediante el bus de datos las líneas desde ADO hasta AD7 del microprocesador, las líneas OO hasta O7 de la memoria EPROM 27256 , y las líneas I/O0 hasta I/O7 de la memoria SRAM 6116.

Conectar las señales desde A12 hasta A15 del microprocesador, con los pines 1,2, 3, 6 del decodificador 74138, según se indica en la Figura 4.

Conectar las señales de ADO hasta AD7 del microprocesador con las entradas de DO hasta D7 del LATCH 74374.

Conectar la señal **CE** de la SRAM y de la EPROM, con la salida correspondiente del decodificador 74138.

Conectar  $\mathbf{WE}$  de la EPROM, con la señal  $\mathbf{WR}$  del microprocesador.

Conectar  $\mathbf{OE}$ , tanto de la EPROM como de la SRAM, con la salida  $\mathbf{RD}$  del microprocesador.

Cuando han sido conectadas todas las señales, como se indicó anteriormente, el diagrama de conexiones quedaría de la siguiente manera:

Figura 4. Esquema de conexión del microprocesador 8085 con memoria EPROM 27256 y memoria SRAM 6116

#### Sabías que...

Se puede conectar al microprocesador más de una memoria de programa o de datos, siempre y cuando se les pueda asignar, de manera independiente un rango de direcciones del microprocesador que no esté ocupado por algún otro dispositivo conectado.

Además hay que tener presente que son limitados los pines de selección que tiene el decodificador para enviar señales que activen determinado dispositivo que el microprocesador escoja. Por lo tanto, para ampliar la cantidad de dispositivos a utilizar en un sistema microprocesado, se podría requerir conectar varios decodificadores en cascada.

#### Preguntas de reflexión

- 1. ¿Qué pasaría si se conecta más de una EPROM al microprocesador?

- 2. ¿En qué caso es conveniente emplear el LATCH 74374 en un sistema microprocesado?

- 3. ¿Cómo quedaría el esquema de conexión completo, indicado en la Figura 4., si se utilizara un microprocesador genérico cuyos pines de dirección y de datos no estén multiplexados?

- 4. ¿En qué casos se utilizaría varios decodificadores 74138 en cascada para un sistema microprocesado?

- 5. ¿Qué otros circuitos integrados serían los sustitutos adecuados para reemplazar el 74374 y el 74138?

#### Bibliografía y Fuentes Electrónicas

- Benítez, C. (2010). issuu. Obtenido de http://issuu.com/microprocesadores/docs/8085\_2

- Massachusetts Institute of Technology. (2015). mit.com. Obtenido de web.mit.edu/6.115/www/document/6116.pdf

1. Del esquema de conexiones de la Figura 5 ¿Qué chip actúa como LATCH?

Figura 5. Conexión de la memoria 6116 con el microprocesador 8085 utilizando un LATCH

- 2. ¿Existen otros chips diferentes al DEMUX 74138 para implementar un decodificador de direcciones para un sistema microprocesado? ¿Cuáles?

- 3. ¿Qué chips se necesitarían para realizar un diagrama de conexiones completo para un sistema microprocesado, que esté compuesto por un microrpocesador 8085, tenga una capacidad de memoria de datos de 6Kb y una capacidad de memoria de programa de 8 Kb?

- 4. Refiérase a la pregunta 3 y elabore cómo quedaría el diagrama de conexión completo para el sistema microprocesado propuesto.

- 5. ¿Cómo quedaría el esquema de conexión de un sistema microprocesado que tenga los siguientes circuitos integrados: microprocesador 8080, memoria de datos 6116 y una memoria de programa 2764? Para solucionar este ejercicio se recomienda revisar el datasheet de cada circuito integrado involucrado.

## El Microprocesador 8085

### Objetivos

- Identificar los bloques y elementos que componen la arquitectura interna del microprocesador 8085.

- Comprender los operaciones y procedimientos necesario para la programación del microprocesador 8085.

- Caracterizar los grupos de instrucciones o nemotécnicos del microprocesador 8085.

#### Introducción

Dentro de este capítulo se han preparado una serie de ejercicios y soluciones prácticas, donde el estudiante aprenderá el manejo de registros, localidades de memoria, repertorios de instrucciones, etc., correspondientes a un sistema microprocesado basado en un microprocesador básico como lo es el Intel 8085.

Se revisarán aspectos claves sobre la arquitectura, descripción de pines y registros del microprocesador 8085, como base para la comprensión de las diferentes actividades que se dan internamente en el mismo, tales como: mover, intercambiar, sumar, deshabilitar o habilitar interrupciones, etc. Además, se realizará el estudio de los ciclos de máquina que se dan al realizar una instrucción, los mismos que involucran la interacción con diferentes dispostivos que forman parte del sistema microprocesado, siempre que estén debidamente conectados y sincronizados con el microprocesador.

Como fuente de información para que los lectores puedan comprender mejor el manejo de instrucciones, se ha tomado como referencia la nomenclatura utilizada por Intel Corporation.

### Caracterización interna del microprocesador 8085

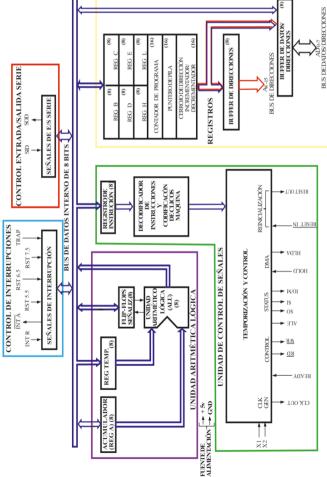

## Arquitectura

El microprocesador 8085 fue presentado por Intel en el año de 1977. Su arquitectura se basa en su antecesor el 8080; e incluye novedades como un generador de impulsos de reloj, controlador de buses, cuatro entradas de interrupción, dos líneas para entrada/salida para información en serie, y un bus de datos y de direcciones multiplexado. Gracias a estas innovaciones al 8085 se lo consideró como un integrado potente, capaz de desarrollar operaciones aritméticas, lógicas y de control.

Internamente el micro 8085 comunica los bloques que lo conforman mediante tres tipos de buses, transmitiendo señales de control, datos o direcciones.

El bus de direcciones, utiliza 16 pines , que desde A15 hasta A8, funcionan de manera independiente, y desde AD7 hasta AD0 están multiplexados, es decir, en un momento en el bus existen datos, y en otro momento direcciones, lo cual permite un ahorro de pines en el microprocesador.

El bus de datos, está formado por 8 bits que utilizan 8 líneas de conexión, desde ADO hasta AD7, para transmitir datos entre los bloques y el exterior, por lo que se trata de un bus bidireccional.

El bus de control, está conformado por un número determinado de líneas, que sirven para la temporización y control de los procesos que realiza el microprocesador, como por ejemplo: leer o escribir en memoria o en puertos y atender interrupciones o ciclos DMA (Direct Memory Access).

El registro de instrucción, es el primer lugar donde se almacenan las instrucciones. Posteriormente, éstas serán interpretadas por el decodificador de instrucciones, que tiene como función identificar cuál micro programa deberá seguir, siempre y cuando el control de reloj le

haya asignado un tiempo de espera para realizar la instrucción. Debido a que este microprocesador no realiza procesos en paralelo, el control de reloj, indica el orden y permite la coordinación de las instrucciones del microprocesador y los periféricos.

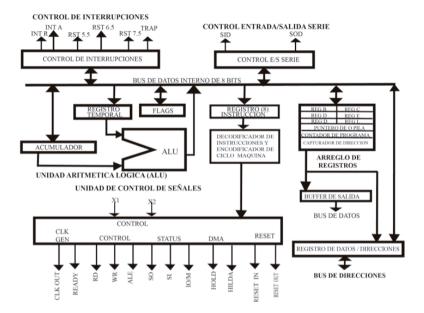

Como se observa en la Figura 6., al microprocesador se lo puede dividir en los siguientes bloques: Registros, Señales de interrupción, señales de E/S, Unidad Aritmética Lógica y Unidad de Control de Señales. Los componentes internos de este grupo de bloques se describen a continuación:

Figura 6. Arqitectura interna del Microprocesador 8085

#### Registros

El microprocesador 8085 posee los siguientes registros:

1. Registros de propósito general: Cuenta con 6 registros de uso general (B, C, D, E, H, L); no tienen una función predefina y se utilizan para guardar datos temporalmente. Individualmente pueden almacenar 8 bits, pero si se necesita mayor capacidad se los puede agrupar en parejas (BC, DE, HL) con capacidades de 16 bits cada una.

Figura 7. Registros de propósito general

| (8)   | (8)   |

|-------|-------|

| REG B | REG C |

| (8)   | (8)   |

| REG D | REG E |

| (8)   | (8)   |

| REG H | REG L |

2. Contador de programa (PC): Es un registro de 16 bits que señala la dirección de memoria de la siguiente instrucción que se va a ejecutar. Su contenido es impredecible e incremental, sin embargo puede ser cambiado según se requiera.

Figura 8. Contador de programa

3. Puntero de pila (SP): Es un registro de 16 bits, conocido como puntero de dato. Señala todo el tiempo a la cima de la pila, que no es nada más que la parte superior del bloque de la memoria RAM, donde se pueden almacenar datos temporalmente.

Figura 9. Puntero de pila

4. Cerrojo de dirección Incrementador/Decrementador: Es un registro de 16 bits que permite aumentar o disminuir en 1 cualquiera de los registros.

Cumple dos funciones que son:

- Primera Función: Selecciona la dirección que va a ser enviada, ya sea al contador de programa, al puntero de pila o cualquiera de los registros de uso general.

- Segunda Función: Almacena la dirección hasta que sea requerida por el bus de dirección interno.

Figura 10. Cerrojo de dirección del micro 8085

CERROJO DE DIRECCIÓN (16) INCREMENTADOR/ DECREMENTADOR

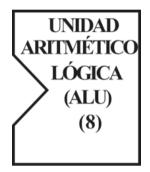

#### Unidad Aritmética Lógica

Está compuesta por:

1. Acumulador: Es un registro de 8 bits, en el cual se almacenarán los datos o el resultado que se obtenga de la ALU (por sus siglas en inglés), así como también puede servir como un registro de propósito general de 8 bits.

Figura 11. Acumulador del 8085

ACUMULADOR (REG A) (8)

2. Registro Temporal: Es un registro de 8 bits que se encarga de recibir los datos provenientes del bus de direcciones interno del microprocesador antes de ser procesado por la unidad aritmética lógica (ALU), conjuntamente con el Registro A.

Figura 12. Registro temporal del 8085

REG TEMP. (8)

3. Flip Flop Señalizadores: Es un registro de 8 bits, que indica el estado en que se encuentra el acumulador, luego de realizarse operaciones aritméticas o lógicas.

Figura 13. Señalizadores de estado del acumulador del 8085

Consta del siguiente formato:

Figura 14. Señalizadores del registro de status del 8085

| $\mathbf{B}_7$ | $\mathbf{B}_{6}$ | $B_5$ | $\mathbf{B_4}$ | $\mathbf{B}_3$ | $\mathbf{B_2}$ | <b>B</b> <sub>1</sub> | $\mathbf{B_0}$ |

|----------------|------------------|-------|----------------|----------------|----------------|-----------------------|----------------|

| S              | Z                |       | AC             |                | P              |                       | CY             |

Donde,

| CY        | = | Acarreo          |

|-----------|---|------------------|

| P         | = | Paridad          |

| AC        | = | Acarreo auxiliar |

| Z         | = | Cero             |

| S         | = | Signo            |

| En blanco | = | Indiferente      |

CY (Señalizador de arrastre), puede tener por valor "1" en dos casos: en una suma, cuando el resultado supera los 8 bits o en una resta, cuando el minuendo sea menor que el sustraendo. Caso contrario tomará el valor de "0".y no se perdería claridad en la oración.

P (Señalizador de paridad), sin considerar el bit de acarreo, cuenta la cantidad de "1s" (unos) de un resultado ubicado en el Acumulador. Cuando éstos estén en número par (paridad par), P=1. En cambio sí están en número impar (paridad impar), P=0.

AC (Señalizador de arrastre auxiliar), busca si existe un acarreo en el proceso de suma de los bits, de la posición 3 (B3) a la posición 4 (B4), pues de ser así, AC= 1. Caso contrario, si no hubiese acarreo, AC=0. De la misma forma que CY, indicaría lo anteriormente descrito, para la suma de los bits desde la posición 7 (B7).

Z (Señalizador de cero), se pone en "1" sólo cuando el resultado (ubicado en el Acumulador) de una operación es cero, de no ser así Z toma el valor de "0".

- S (Señalizador de signo) se encarga de identificar cuándo un resultado es negativo o positivo basándose en el MSB. Toma el resultado del acumulador de izquierda a derecha, si el primer valor encontrado es "1" se trata de un valor negativo y S tomará el valor de "1". Caso contrario, si el valor encontrado es "0" se trata de un número positivo y S se pondrá en "0".

- 4. Unidad Aritmética lógica (ALU): Es un circuito lógico combinatorio, que se encarga de realizar las operaciones aritméticas, lógicas y de desplazamiento, cuyo resultado, posteriormente es enviado hasta el acumulador.

Figura 15. Unidad aritmética lógica del 8085

#### Unidad de control de Señales

1. Registro de instrucciones: Es un registro de 8 bits que retiene el código de operación antes de ser interpretado por el decodificador de instrucciones y codificador de ciclos de máquina.

Figura 16. Registro de instrucción del 8085

2. Decodificador de instrucciones y codificación de ciclos de maquina: Cuando esté en ejecución el microprocesador, procederá a la búsqueda de instrucciones, cuyo código de operación (OP) será primeramente transferido al registro de instrucciones.

El decodificador de instrucciones permite, controlar los registros, la unidad aritmética lógica (ALU), buffer de datos y de dirección, siempre y cuando se le haya asignado el temporizador del control de reloj.

Figura 17. Decodificador de instrucciones del 8085

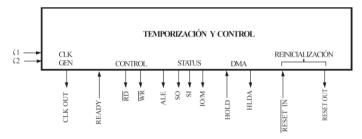

3. Temporizador y Control: Para que exista un control y sincronización dentro del chip, el microprocesador 8085 posee un control de reloj que permite producir señales para control interno y externo de los componentes, que se activa mediante el uso del cristal de cuarzo.

Figura 18. Temporización y control del 8085

# Control de Interrupciones

Interrupciones: En cuanto a las interrupciones, el microprocesador 8085 posee 5 tipos que son:

TRAP Guarda el contador del programa en la pila y salta a la posición 0024H, una característica importante es que no puede ser inhabilitada (no enmascarable)

RST 7.5 Guarda la pila en el contador del programa y salta a la posición 003CH

RST 6.5 Guarda la pila en el contador del programa y salta a la posición 0034H

RST 5.5 Guarda la pila en el contador del programa y salta a la posición 002CH

INTR Busca una instrucción de una fuente externa

Tabla 4. Interrupciones hardware del 8085

| Nombre  | Prioridad | Dirección (1) a la que se<br>bifurca cuando ocurre<br>la interrupción | Tipo de disparo                                                |

|---------|-----------|-----------------------------------------------------------------------|----------------------------------------------------------------|

| TRAP    | 1         | 0024H                                                                 | Flanco de subida AND<br>nivel alto hasta que sea<br>muestreada |

| RST 7.5 | 2         | 003CH                                                                 | Flanco de subida<br>(cerrojo)                                  |

| RST 6.5 | 3         | 0034H                                                                 | Nivel alto hasta que sea<br>muestreada                         |

| RST 5.5 | 4         | 002CH                                                                 | Nivel alto hasta que sea<br>muestreada                         |

| INTR    | 5         | (2)                                                                   | Nivel alto hasta que sea<br>muestreada                         |

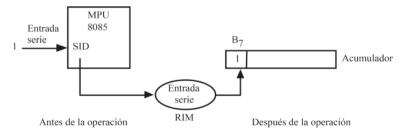

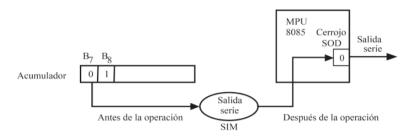

### Control de Entrada/salida serie

La entrada SOD y la salida SID, son utilizadas para transferir datos binarios desde y hacia los dispositivos externos de comunicación.

1. SID (Serial Input Data): Se lo puede utilizar como un probador de propósito general para lo cual se utiliza la instrucción RIM.

Figura 19. Instrucción RIM del 8085 para entrada serie

2. SOD (Serial Output Data): Se lo puede utilizar como salida de control de 1 bit, utilizando la instrucción SIM.

Figura 20. Instrucción SIM del 8085 para salida serie

#### Descripción de pines

El microprocesador Intel 8085, tiene un tipo de encapsulado DIP de 40 pines, de los cuales 8, son para el bus de direcciones (de A8 hasta A15) y trabajan de forma independiente. Mientras que los pines para el bus de datos (de AD0 hasta AD7), están multiplexados, lo que requiere del pin ALE, para poder utilizar externamente los bits de direcciones o datos, en el momento que éstos sean requeridos.

Los pines RD y WR, listados en la Tabla 5, permiten enviar o recibir datos procedentes de los dispositivos conectados al microprocesador.

Los pines del microprocesador 8085 se pueden agrupar de la siguiente manera:

- Pines A8 A15 Bus de direcciones (Independiente)

- Pines AD0 AD7 Bus de direcciones y datos (Compartido)

- Pines para el bus de control

- Pines para la frecuencia de reloj

- Pines para el manejo de interrupciones

- Pines de alimentación

A continuación se describe la función que cumple cada pin, de acuerdo a la señal que representa, siguiendo las especificaciones que el fabricante establece en el datasheet del componente.

Tabla 1. Descripción de pines del microprocesador 8085

32

33

34

35

RD

S1

IO/M

READY

| Microprocesador 8085 |                                                              |                                                                 |  |  |  |  |

|----------------------|--------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

|                      | 35<br>39<br>10<br>9<br>8<br>7<br>6<br>36<br>1<br>1<br>2<br>2 | AD3                                                             |  |  |  |  |

| PIN                  | NOMBRE                                                       | DESCRIPCIÓN                                                     |  |  |  |  |

| 1                    | X1                                                           | Permite conectar el cristal de cuarzo para que funcione el      |  |  |  |  |

| 2                    | X2                                                           | control de reloj                                                |  |  |  |  |

| 3                    | RESET OUT                                                    | Permite inicializar los periféricos                             |  |  |  |  |

| 4                    | SOD                                                          | Salida serie                                                    |  |  |  |  |

| 5                    | SID                                                          | Entrada serie                                                   |  |  |  |  |

| 6                    | TRAP                                                         | Entrada de interrupción no enmascarable ( No se deshabilita )   |  |  |  |  |

| 7                    | RST 7.5                                                      |                                                                 |  |  |  |  |

| 8                    | RST 6.5                                                      | Entradas de interrupción                                        |  |  |  |  |

| 9                    | RST 5.5                                                      |                                                                 |  |  |  |  |

| 10                   | INTR                                                         | Entrada de interrupción (externa)                               |  |  |  |  |

| 11                   | INTA                                                         | Reconocimiento de interrupción                                  |  |  |  |  |

| 12-19                | AD0 – AD7                                                    | Bus de direcciones y datos (Compartido)                         |  |  |  |  |

| 20                   | GND                                                          | Conexión a tierra                                               |  |  |  |  |

| 21-28                | A8 – A15                                                     | Bus de direcciones (independiente)                              |  |  |  |  |

| 29                   | SO                                                           | Bit de estado                                                   |  |  |  |  |

| 30                   | ALE                                                          | Funciona como cerrojo 0 Habilita datos y 1 habilita direcciones |  |  |  |  |

| 21                   | WR                                                           | Escritura - Funciona con salida 0                               |  |  |  |  |

| 31                   | VVII                                                         | Escritura Turiciona con sanda o                                 |  |  |  |  |

Lectura – Funciona con salida 0

1 operaciones con puertos, 0 operaciones con memoria

Sincroniza memorias y periféricos de menor velocidad

Bit de estado

| 36 | RESET IN | Inicializa el microprocesador cuando está en 0                           |

|----|----------|--------------------------------------------------------------------------|

| 37 | CLK OUT  | Salida de la señal del reloj interno                                     |

| 38 | HLDA     | Reconocimiento de HOLD                                                   |

| 39 | HOLD     | Funciona para que los buses tengan alta impedancia para el manejo de DMA |

| 40 | VCC      | Fuente de alimentación 5 voltios                                         |

#### Introducción a la programación del microprocesador 8085

#### Ciclos de ejecución de las instrucciones

Cuando llegan instrucciones al microprocesador, éste no las ejecuta de manera inmediata, pues requiere de múltiples tareas y operaciones para que la información que se envía, llegue al destino correcto o viceversa. A este proceso se le denomina ciclo de instrucción.

Los ciclos de ejecución de las instrucciones se componen de las siguientes características:

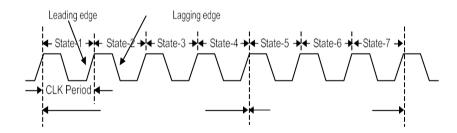

Diagrama de Temporización.- Es la representación gráfica de los ciclos de instrucción que se requieren ejecutar; esta representación está constituida por T Estados.

Figura 21. Diagrama de Temporización

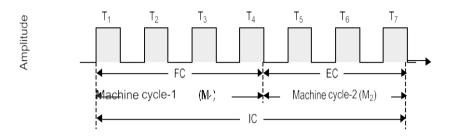

Ciclo de Instrucción.- Es el tiempo que se necesita para que el microprocesador ejecute una instrucción y está compuesto por uno o varios ciclos de máquina.

Ciclo de Máquina.- Denota una actividad específica del microprocesador y está compuesta por varios estados.

Figura 22. Ciclo de Máquina

Estados.- Son los periodos de la señal de reloj temporizados por el microprocesador y que permiten que se lleven a cabo los ciclos de máquina y los ciclos de instrucción.

A continuación en la Tabla 6, se indican todos los ciclos de máquina con los que cuenta el microprocesador 8085.

Tabla 6. Ciclos de máquina del microprocesador 8085

| ESTADO DE SEÑALES                               |                                                |   |   |   |   |   |  |  |  |  |  |  |

|-------------------------------------------------|------------------------------------------------|---|---|---|---|---|--|--|--|--|--|--|

| El ciclo de la máquina                          | El ciclo de la máquina IO / M S1 S0 RD WR INTA |   |   |   |   |   |  |  |  |  |  |  |

| Fetch (opcode)                                  | 0                                              | 1 | 1 | 0 | 1 | 1 |  |  |  |  |  |  |

| Memoria de lectura                              | 0                                              | 1 | 0 | 0 | 1 | 1 |  |  |  |  |  |  |

| Escritura de memoria                            | 0                                              | 0 | 1 | 1 | 0 | 1 |  |  |  |  |  |  |

| Lectura de E/S (I/O)                            | 1                                              | 1 | 0 | 0 | 1 | 1 |  |  |  |  |  |  |

| Escritura de E/S (I/OW)                         | 1                                              | 0 | 1 | 1 | 0 | 1 |  |  |  |  |  |  |

| Acusar de INTR (INTA)                           | 1                                              | 1 | 1 | 1 | 1 | 0 |  |  |  |  |  |  |

| BUS Inactivo (BI)                               | 0                                              | 1 | 0 | 1 | 1 | 1 |  |  |  |  |  |  |

| ACK de RST                                      | 1                                              | 1 | 1 | 1 | 1 | 1 |  |  |  |  |  |  |

| Detener                                         | Z                                              | 0 | 0 | Z | Z | 1 |  |  |  |  |  |  |

| Mantenga                                        | Z                                              | Х | Х | Z | Z | 1 |  |  |  |  |  |  |

| X → Z Indeterminado → estado de impedancia alta |                                                |   |   |   |   |   |  |  |  |  |  |  |

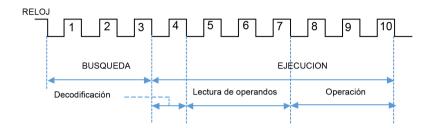

El proceso que realiza el microprocesador para realizar las instrucciones consta de dos fases fundamentales:

- Fase de búsqueda.

- Fase de ejecución.

Figura 23. Fases de un ciclo de instrucción

Como se puede apreciar en la Figura 23, para ejecutar una instrucción, el microprocesador comienza con una fase de búsqueda del primer byte de la instrucción, que se conoce con el nombre de código de operación, para luego dependiendo del tipo de instrucción que ejecuta, realizar otros ciclos de máquina correspondientes.

# Ciclos de máquina

A continuación, se explicarán algunos de los ciclos de máquina más comunes, en la mayoría de instrucciones del microprocesador 8085.

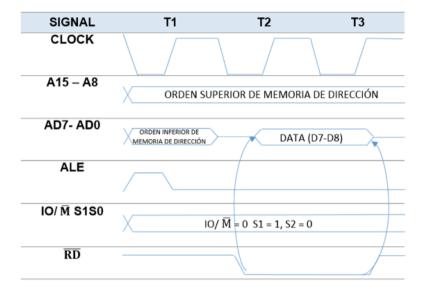

## Operación búsqueda de código de operación (opcode fetch)

Es el primer ciclo de máquina a ejecutarse cuando se realiza cualquier instrucción, comúnmente denominado OPCODE FETCH. Este ciclo de máquina cumple la función de traer el código de operación de la instrucción que se ejecuta, desde la memoria.

El ciclo de búsqueda está compuesto por 4 estados de tiempo, cuyos 3 primeros estados son para obtener el código de la operación de la instrucción, mientras que el último estado sirve para decodificar y ejecutar la instrucción.

Algunas instrucciones, requieren de 6 estados de tiempo, para realizar la búsqueda del código de operación.

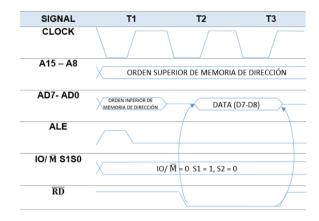

Tabla 7. Operación búsqueda de código de operación (opcode fetch)

# Operación de ciclo lectura de memoria

Para realizar esta operación, el microprocesador temporiza algunas de sus señales, tal como se indica en la Tabla 8., para, a partir de T2, activar la señal RD' hacia el estado bajo, de tal manera que en el bus multiplexado AD0....AD7, sea colocado el dato para su lectura hacia el microprocesador.

Tabla 8. Operación de ciclo lectura de memoria

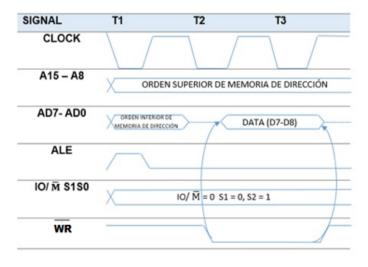

## Operación de ciclo escritura de memoria

Para realizar esta operación, el microprocesador temporiza algunas de sus señales, tal como se indica en la Tabla 9., para a partir de T2, activar la señal WR hacia el estado bajo, de tal manera que en el bus multiplexado AD0....AD7, sea colocado el dato, desde el bus de datos interno del microprocesador, hacia la celda de memoria correspondiente.

Tabla 9. Operación de ciclo escritura de memoria

#### Modos de direccionamiento

Los modos de direccionamiento son procesos particulares que se realizan de manera general, para un grupo determinado de instrucciones.

Los cinco modos de direccionamiento, que presentan las instrucciones del microprocesador 8085, son:

## Direccionamiento implicado

No se necesita ninguna interacción entre los diferentes elementos que componen el microprocesador. Las instrucciones que tiene éste tipo de direccionamiento afectan solamente un elemento.

## Direccionamiento de registro

Las instrucciones que operan con este modo de direccionamiento, involucran la interacción solamente de cualquiera de los registros de 8 o 16 bits con que cuenta el microprocesador 8085.

Figura 24. Instrucción ADD C, modo de direccionamiento de registro

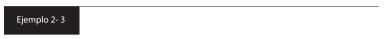

#### Direccionamiento inmediato

Este modo de direccionamiento presenta la particularidad de que el dato necesario para ejecutar la instrucción, se encuentra ubicado inmediatamente a continuación del código de operación de la misma instrucción.

Figura 25. Instrucción ADI 08H, modo de direccionamiento inmediato

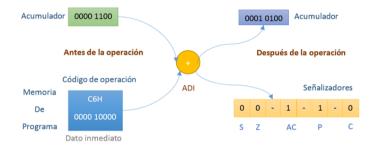

#### Direccionamiento directo

En éste modo de direccionamiento, luego del código de operación de la instrucción, se encuentran 2 bytes, que se utilizan en conjunto como puntero de memoria, para leer o escribir un dato específico, requerido para la ejecución de una instrucción dada.

Figura 26. La Instrucción LDA 0200H, modo de direccionamiento directo.

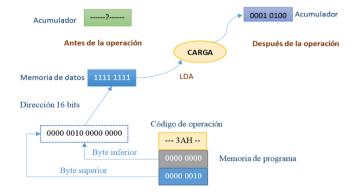

### Direccionamiento indirecto de registro

Las instrucciones con modo de direccionamiento indirecto de registro, utilizan los registros pares H y L como puntero de memoria, para leer o escribir un dato específico, requerido para la ejecución de una instrucción dada.

Repertorio de instrucciones del microprocesador 8085

En el microprocesador 8085, las instrucciones son almacenadas como bytes de 8 bits en el área de memoria de programa. Utiliza instrucciones de 1, 2 y 3 bytes. El primer byte de la instrucción es el código de operación, que indica cuál de las instrucciones del microprocesador debe ejecutarse. El microprocesador 8085 tiene 239 instrucciones almacenadas. La MPU identifica los códigos de operación cuando están en forma binaria de 8 bits.

El diseño de pastilla, ya trae incorporado de forma permanente el grupo de instrucciones a las cuales responderá la MPU 8080 y 8085. Cabe mencionar que tanto el microprocesador 8080 y el 8085 utilizan los mismos códigos de operación. Además el 8085 contiene dos instrucciones adicionales al conjunto de instrucciones del MPU 8080.

Intel Corporation, agrupa las instrucciones del microprocesador 8080/8085 en categorías de acuerdo a sus funciones, quedando establecido de la siguiente manera:

- 1. Grupo de transferencia de datos

- 2. Grupo aritmético

- 3. Grupo lógico

- 4. Grupo de bifurcaciones

- 5. Grupo de pila, E/S y de control máquina.

En el Apéndice C se indica la nomenclatura que se utilizará para representar las operaciones de las instrucciones del microprocesador, tomando como referencia el formato utilizado por Intel Corporation.

## Grupo de transferencia de datos

Un grupo de instrucciones indica el conjunto de acciones que puede entender y ejecutar un microprocesador. Uno de los grupos que engloba estas instrucciones, es el grupo de transferencia de datos, que se estudia en este capítulo.

El conjunto de instrucciones de transferencia de datos, entre registros o entre posiciones de memoria y registros, incluye operaciones de transferir, intercambiar, cargar y almacenar.

El repertorio de instrucciones para la transferencia de datos del microprocesador 8085 se detalla en la Tabla 10.

| DESCRIPCIÓN                                | CÓDIGO DE<br>OPERACIÓN | NEMOTÉCNICO       | BYTES DE<br>INSTRUCCIÓN | ESTADOS | CICLOS<br>DE<br>MÁQUINA |

|--------------------------------------------|------------------------|-------------------|-------------------------|---------|-------------------------|

|                                            | TRANSFEREN             | CIA DE REGISTRO A | REGISTRO                |         |                         |

| MOVIMIENTOS AL<br>REGISTRO A               |                        |                   |                         |         |                         |

| Mueva el contenido del Reg.<br>B al Reg. A | 78                     | MOV A, B          | 1                       | 4       | 1                       |

| Mueva el contenido del Reg.<br>C al Reg. A | 79                     | MOV A, C          | 1                       | 4       | 1                       |

| Mueva el contenido del Reg.<br>D al Reg. A | 7A                     | MOV A, D          | 1                       | 4       | 1                       |

| Mueva el contenido del Reg.<br>E al Reg. A | 7B                     | MOV A, E          | 1                       | 4       | 1                       |

| Mueva el contenido del Reg.<br>H al Reg. A | 7C | MOV A, H | 1 | 4 | 1 |

|--------------------------------------------|----|----------|---|---|---|

| Mueva el contenido del Reg.<br>L al Reg. A | 7D | MOV A, L | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>A al Reg. A | 7F | MOV A, A | 1 | 4 | 1 |

| MOVIMIENTOS AL<br>REGISTRO B               |    |          |   |   |   |

|--------------------------------------------|----|----------|---|---|---|

| Mueva el contenido del Reg.<br>B al Reg. B | 40 | MOV B, B | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>C al Reg. B | 41 | MOV B, C | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>D al Reg. B | 42 | MOV B, D | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>E al Reg. B | 43 | MOV B, E | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>H al Reg. B | 44 | MOV B, H | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>L al Reg. B | 45 | MOV B, L | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>A al Reg. B | 47 | MOV B, A | 1 | 4 | 1 |

| MOVIMIENTOS AL<br>REGISTRO C               |    |          |   |   |   |

|--------------------------------------------|----|----------|---|---|---|

| Mueva el contenido del Reg.<br>B al Reg. C | 48 | MOV C, B | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>C al Reg. C | 49 | MOV C, C | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>D al Reg. C | 4A | MOV C, D | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>E al Reg. C | 4B | MOV C, E | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>H al Reg. C | 4C | MOV C, H | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>L al Reg. C | 4D | MOV C, L | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>A al Reg. C | 4F | MOV C, A | 1 | 4 | 1 |

| MOVIMIENTOS AL<br>REGISTRO D               |    |          |   |   |   |

|--------------------------------------------|----|----------|---|---|---|

| Mueva el contenido del Reg.<br>B al Reg. D | 50 | MOV D, B | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>C al Reg. D | 51 | MOV D, C | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>D al Reg. D | 52 | MOV D, D | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>E al Reg. D | 53 | MOV D, E | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>H al Reg. D | 54 | MOV D, H | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>L al Reg. D | 55 | MOV D, L | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>A al Reg. D | 57 | MOV D, A | 1 | 4 | 1 |

| MOVIMIENTOS AL<br>REGISTRO B               |    |          |   |   |   |

|--------------------------------------------|----|----------|---|---|---|

| Mueva el contenido del Reg.<br>B al Reg. E | 58 | MOV E, B | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>C al Reg. E | 59 | MOV E, C | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>D al Reg. E | 5A | MOV E, D | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>E al Reg. E | 5B | MOV E, E | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>H al Reg. E | 5C | MOV E, H | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>L al Reg. E | 5D | MOV E, L | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>A al Reg. E | 5F | MOV E, A | 1 | 4 | 1 |

| MOVIMIENTOS AL<br>REGISTRO H               |    |          |   |   |   |

|--------------------------------------------|----|----------|---|---|---|

| Mueva el contenido del Reg.<br>B al Reg. H | 60 | MOV H, B | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>C al Reg. H | 61 | MOV H, C | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>D al Reg. H | 62 | MOV H, D | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>E al Reg. H | 63 | MOV H, E | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>H al Reg. H | 64 | MOV H, H | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>L al Reg. H | 65 | MOV H, L | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>A al Reg. H | 67 | MOV H, A | 1 | 4 | 1 |

| MOVIMIENTOS AL<br>REGISTRO L               |    |          |   |   |   |

|--------------------------------------------|----|----------|---|---|---|

| Mueva el contenido del Reg.<br>B al Reg. L | 68 | MOV L, B | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>C al Reg. L | 69 | MOV L, C | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>D al Reg. L | 6A | MOV L, D | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>E al Reg. L | 6B | MOV L, E | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>H al Reg. L | 6C | MOV L, H | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>L al Reg. L | 6D | MOV L, L | 1 | 4 | 1 |

| Mueva el contenido del Reg.<br>A al Reg. L | 6F | MOV L, A | 1 | 4 | 1 |

| TRANSFERENCIA DE REGISTRO INMEDIATA |    |             |   |   |   |  |  |  |

|-------------------------------------|----|-------------|---|---|---|--|--|--|

| Mueva data al Registro A            | 3E | MVI A, data | 2 | 7 | 2 |  |  |  |

| Mueva data al Registro B            | 06 | MVI B, data | 2 | 7 | 2 |  |  |  |

| Mueva data al Registro C            | 0E | MVI C, data | 2 | 7 | 2 |  |  |  |

| Mueva data al Registro D            | 16 | MVI D, data | 2 | 7 | 2 |  |  |  |

| Mueva data al Registro E            | 1E | MVI E, data | 2 | 7 | 2 |  |  |  |

| Mueva data al Registro H            | 26 | MVI H, data | 2 | 7 | 2 |  |  |  |

| Mueva data al Registro L            | 2E | MVI L, data | 2 | 7 | 2 |  |  |  |

|                          | TRANSFEREN | ICIA A MEMORIA II | NMEDIATA |    |   |

|--------------------------|------------|-------------------|----------|----|---|

| Mueva data a la memoria* | 35         | MVI M, data       | 2        | 10 | 2 |

| CARGAR REGISTRO PAR INMEDIATO                |    |                |   |    |   |  |  |  |

|----------------------------------------------|----|----------------|---|----|---|--|--|--|

| Cargue el apuntador de la<br>pila con data16 | 31 | LXI SP, data16 | 3 | 10 | 3 |  |  |  |

| Cargue los registros B y C con<br>data16     | 01 | LXI B, data16  | 3 | 10 | 3 |  |  |  |

| Cargue los registros D y E con<br>data16     | 11 | LXI D, data16  | 3 | 10 | 3 |  |  |  |

| Cargue los registros H y L con<br>data16     | 21 | LXI H, data16  | 3 | 10 | 3 |  |  |  |

|                                          | CAR | GAR H Y L DIRECT | 0 |    |   |

|------------------------------------------|-----|------------------|---|----|---|

| Cargue H y L con el<br>contenido de addr | 2A  | LHLD addr        | 3 | 16 | 5 |

|                                                  | CARGAR | ACUMULADOR DI | RECTO |    |   |

|--------------------------------------------------|--------|---------------|-------|----|---|

| Cargue el Reg. A con el<br>contenido de addr     | 3A     | LDA addr      | 3     | 13 | 4 |

| Cargue Reg. A con el<br>contenido de la posición |        |               |       |    |   |

| CARGA INDIRECTO EL ACUMULADOR                    |    |          |   |    |   |  |  |  |

|--------------------------------------------------|----|----------|---|----|---|--|--|--|

| de memoria definida por<br>B y C                 | 0A | LDA addr | 3 | 13 | 4 |  |  |  |

| Cargue Reg. A con el<br>contenido de la posición |    |          |   |    |   |  |  |  |

| de memoria definida por<br>D y E                 | 1A | LDAX D   | 1 | 7  | 2 |  |  |  |

| Almacena Reg. A en la<br>posición de memoria     |    |          |   |    |   |  |  |  |

| ALMACENA INDIRECTO EL ACUMULADOR                                            |    |        |   |   |   |  |

|-----------------------------------------------------------------------------|----|--------|---|---|---|--|

| Definida por los Reg. B y C                                                 | 02 | STAX B | 1 | 7 | 2 |  |

| Almacena Reg. A en la<br>posición de memoria<br>definida por los Reg. D y E | 12 | STAX D | 1 | 7 | 2 |  |

|                                    | ALMACEN | A ACUMULADOR D | DIRECTO |    |   |

|------------------------------------|---------|----------------|---------|----|---|

| Almacena Reg. A en la<br>dirección | 32      | STA addr       | 3       | 13 | 4 |

| ALMACENA H Y L DIRECTO                  |    |           |   |    |   |

|-----------------------------------------|----|-----------|---|----|---|

| Almacena Regs. H y L en la<br>dirección | 22 | SHLD addr | 3 | 16 | 5 |

Nota: addr= Dirección de memoria (16 bits); data= Dato de 8 bits (un Byte); data16= Un dato de 16 bits (2 Bytes); \*= La dirección de memoria (M) está especificada por el contenido de los registros H y L

A continuación se detallan cada una de las instrucciones del grupo de transferencia de datos.

MOV r1, r2 (Transfiere registro)

| Nemotécnico                  | MOV r1, r2  |

|------------------------------|-------------|

| Simbología de funcionamiento | (r1) ← (r2) |

| Modo de direccionamiento     | registro    |

| Señalizadores afectados      | Ninguno     |

| Ciclos                       | 1           |

| Estados                      | 4           |

Descripción del funcionamiento: El contenido del registro r2 es transferido al registro r1.

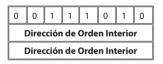

Bytes de Instrucción:

| 01 | DDD  | SSS |

|----|------|-----|

|    | DATO |     |

MOV r, M (Transfiere de memoria)

| Nemotécnico                  | MOV r, M              |

|------------------------------|-----------------------|

| Simbología de funcionamiento | (r) ← ((H) (L))       |

| Modo de direccionamiento     | Indirecto de registro |

| Señalizadores afectados      | Ninguno               |

| Ciclos                       | 2                     |

| Estados                      | 7                     |

Descripción del funcionamiento: El contenido de la posición de memoria cuya dirección está indicada a través de los registros H y L es transferido al registro r

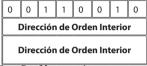

Bytes de Instrucción:

| 01 | DDD  | 110 |

|----|------|-----|

|    | DATO |     |

MOV M, r (Transfiere a memoria)

| Nemotécnico                  | MOV M, r              |

|------------------------------|-----------------------|

| Simbología de funcionamiento | ((H) (L)) ← (r)       |

| Modo de direccionamiento     | Indirecto de registro |

| Señalizadores afectados      | Ninguno               |

| Ciclos                       | 2                     |

| Estados                      | 7                     |

Descripción del funcionamiento: El contenido del registro  ${\bf r}$  es transferido a la posición de memoria cuya dirección está en los registros H y L.

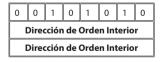

Byte de instrucción:

| 01110 | SSS |

|-------|-----|

| DATO  |     |

# MVI r, dato (Transferencia inmediata)

| Nemotécnico                  | MVI r, dato  |

|------------------------------|--------------|

| Simbología de funcionamiento | (r) ← (dato) |

| Modo de direccionamiento     | Inmediato    |

| Señalizadores afectados      | Ninguno      |

| Ciclos                       | 2            |

| Estados                      | 7            |

Descripción del funcionamiento: Transfiere el dato que se encuentra en el byte 2 de la instrucción en el registro r.

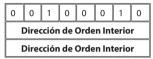

Bytes de instrucción:

| CÓDIGO DE OPERACIÓN | 0 | 0 | D | D  | D  | 1 | 1 | 0 |

|---------------------|---|---|---|----|----|---|---|---|

| BYTE 2              |   |   |   | D/ | ТО |   |   |   |

# MVI M, dato (Transfiere a memoria inmediata)

| Nemotécnico                  | MVI M, dato                     |  |  |  |

|------------------------------|---------------------------------|--|--|--|

| Simbología de funcionamiento | ((H) (L))← (byte 2)             |  |  |  |

| Modo de direccionamiento     | Inmediata indirecto de registro |  |  |  |

| Señalizadores afectados      | Ninguno                         |  |  |  |

| Ciclos                       | 3                               |  |  |  |

| Estados                      | 10                              |  |  |  |

Descripción del funcionamiento: El dato contenido en el byte 2 de la instrucción, es transferido a la posición de memoria cuya dirección está indicada por los registros H y L

Bytes de instrucción:

| CÓDIGO DE OPERACIÓN | 0 | 0 | 1 | 1  | 0  | 1 | 1 | 0 |

|---------------------|---|---|---|----|----|---|---|---|

| BYTE 2              |   |   |   | D/ | то |   |   |   |

LXI rp, dato 16 (Carga registro par inmediato)

| Nemotécnico                  | LXI rp, dato 16                     |

|------------------------------|-------------------------------------|

| Simbología de funcionamiento | (rh) ← (byte 3),<br>(rl) ← (byte 2) |

| Modo de direccionamiento     | Inmediato                           |

| Señalizadores afectados | Ninguno |

|-------------------------|---------|

| Ciclos                  | 3       |

| Estados                 | 10      |